International Journal of Engineering and Innovative Technology (IJEIT)

Volume 3, Issue 4, October 2013

# Non-Uniform Traffic Performance of Multi-Class Scheduling Technique with Dual Threshold

A. A. Abdul Rahman<sup>1</sup>, K. Seman<sup>2</sup>, K. Saadan<sup>3</sup>, A. Azman<sup>4</sup>, F. Salim<sup>5</sup>

Telekom Research & Development, <sup>2, 3</sup>Universiti Sains Islam Malaysia, <sup>4</sup>Universiti Putra Malaysia, <sup>5</sup>Universiti Teknologi Malaysia

Abstract— Network with many types of traffic such as video conferencing, audio and data transfer requires a specific Quality of Services (QoS) to maintain their performance. It is crucial for the switch designer to guarantee QoS for all applications. In this paper, a new way of handling multi-class traffic has been presented. The analysis is done on 16x16 switch with two priority traffic classes and dual threshold setting. Dual threshold setting is implemented on the 16x16 switch to ensure a better control on the priority setting for both classes. In the reality, switch application operates under non-uniform traffic condition. Thus, the analysis in this paper is done under two different kind of non-uniform traffic patterns which are known as the hot-spot pattern and Community-of-Interest (COI) pattern. The proposed method is simulated to show that the delay performance of the non-uniform traffic patterns for the proposed switch architecture has been improved.

*Index Terms*— QoS, multi-class, non-uniform traffic, scheduling technique.

#### I. INTRODUCTION

The role of communication is rapidly growing in today's world. With the advent of the Internet and the subsequent proliferation of Internet technologies, multimedia applications have been given a whole new lease of life.

With more activities such as businesses and educations are relying on a high-speed network, it is expected that high-speed network can provide a guaranteed quality of services (QoS). This requirement has led to the design of high speed switches and routers with high aggregate bandwidth.

Previous analysis on fast packet switches with input queues provides approximation techniques for the switches operating with only a single priority class [2]-[11]. In a single priority class, all cells are served equally without any consideration to high-priority cells and low priority cells. In this situation, high-priority cells will suffer a long delay in the queue. This will contribute to poor application performance. To overcome this problem, a multi-class switch has been introduced to cater the need of various applications with different QoS requirement for the network. One of the best methods to satisfying these requirements is the use of a fast packet switching technology based on priority [1],

[12]-[14].

In most multi-class switches, high-priority class will be served first compared to the low-priority class [15]-[17]. This situation has led to the starvation problem in low priority class. To reduce the starvation problem, a threshold setting is introduced into the scheduling phase. The threshold setting will increase the probability of serving for the low-priority class. In other words, the low-priority class can still be served even in the presence of high-priority class. In this paper, dual threshold setting is proposed to eliminate the starvation problem as well as to maintain the QoS requirements. The proposed scheduling technique is then applied to multi-class switch architecture to ensure the total delay for every class can be optimized.

Under a uniform traffic, the cells are distributed equally to all the output ports. Meanwhile, under non-uniform traffic, the cells are unevenly distributed to the output ports. There have been various studies on non-uniform traffic patterns [18]-[26]. The patterns used throughout this paper are the hot-spot traffic [22]-[26] which consist of single output port and the community-of-interest (COI) traffic [24]-[26], which consists a group of output ports.

This paper attempts to analyze the performance of input queue multi-class priority switch under non-uniform traffic, while taking into account the influence of different classes of services when the threshold is introduced. At the same time, the switch operation will be illustrated in terms of high and low priority traffic loads with separate queues. The switch performance is then analyzed in terms of average delay for high-priority class and low priority class in the presence of dual thresholds under non-uniform traffic.

This paper is organized as follows. In section II, the system description and the model proposed are discussed briefly. Section III will present the analysis of the proposed scheduling technique and multi-class switch architecture in terms of the total mean delay. Section IV is devoted to the simulation results in different probability values of threshold serving class,  $P_{TSC0}$  and the number of queue cell,  $N_b$ . Finally, section V will provide a brief conclusion from the findings.

#### International Journal of Engineering and Innovative Technology (IJEIT) Volume 3, Issue 4, October 2013

#### II. SYSTEM DESCRIPTION AND MODELING

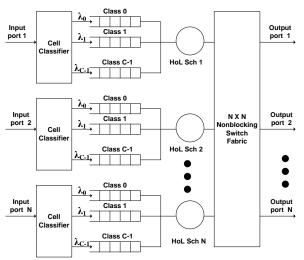

Fig. 1 shows the proposed N ports' multi-class switch architecture. The multi-class switch is serving C-I classes of traffics. The delay requirement is defined by  $D_j$  with j = 0, 1, 2... C-1 and  $D_0 > D_1 > D_2 > ..... > D_{C-1}$ . This mean, the delay requirement for Class 1 is more stringent than Class 0. Thus, cells that queue in Class 0 have the lowest priority and cells that queue in Class C-I have the highest priority. These delay requirements is set based on QoS requirement and is different depending upon the type of applications.

Fig. 1: Multi-class switch architecture.

In this design, time slot is used to represent the time of one cell arrive in the input port or one cell departure from the output port. The time slot,  $T_s$  is set to be equal to the time needed to process a single cell when the server is idle.

The cell is arriving at each input port in every time slot according to the independent Bernoulli distributions. The cell is then classified based on its delay requirement. In this architecture, the class of the cell is located in the header. An arrival cell for Class j ( $\lambda_j$ ) is queue in the infinite First-In-First-Out (FIFO) buffer before it is served.

At each time slot, the switch attempts to serve the cells at Head of Line (HoL) of each input queue. In the case when there are different classes of cells waiting at HoL, the HoL scheduler (HoL Sch) will select a cell with high-priority to be served. The lose cells in the contention must be waited in the queue. The numbers of queue cells will be increased if there are new incoming cells to the queue.

The threshold setting is introduced to give privileges to the cells in the lower-priority class. The number of queue cell,  $N_{bj}$  and the probability on threshold serving the low-priority cell has been used in this architecture as the threshold setting. The number of queue cell parameter,  $N_{bj}$  is chosen because of the limited buffer size available in the practical design. The need to adjust the  $N_{bj}$  is necessary in order to reduce the packet loss if the buffer is full. This parameter is then adjusted based on the size of buffer used to stored cells in Class j.

The probability on threshold serving the low-priority cell,  $P_{TSCj}$  is the probability to serve the Class j when the  $N_{bj}$  parameter threshold is met. Parameter  $P_{TSCj}$  is chosen to control the variation of delay between high-priority and low-priority cell based on the high-priority QoS requirements. This is necessary in order to achieve a better performance for Class j cells. In case where both threshold values are met, the switch will select the cell from class where the threshold is trigger even in the presence of higher-priority cells.

#### III. SIMULATION MODEL AND ANALYSIS

#### A. Simulation Model

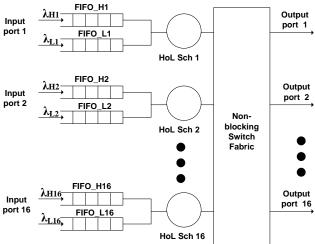

16 x 16 switches architecture with two classes for every input port is used as the simulation model. The simulation model is developed to evaluate the performance of the proposed switch under dual threshold's setting. Class 0 is used to classify the low-priority buffer for non-real-time data. Meanwhile, Class 1 is used to represent the high-priority buffer for real-time data.

Fig. 2 shows the switch architecture for input queue multi-class switch with separate buffer for each class. The arrival cells are stored in different FIFO based on their classes. The HoL scheduler will choose one cell from HoL FIFO classes at every port to be forwarded to switch fabric. The cells will then contend with each other to gain access for departure.

Fig. 2: Switch architecture for input buffer multi-class switch.

The proposed switch operates at the time slotted transmission to process each cell. Each time slot will consist of three phases, which are known as arrival, scheduler and departure.

In the arrival phase, the incoming packet is segmented into fixed size packet and is known as cells. The cells are then aligned for synchronization. In time slot t, cells from Class 1 and Class 0 will be arrived in the input port according to the Bernoulli distribution with probability of  $\lambda H_i$  and  $\lambda L_i$  respectively. The total traffic load ( $\lambda$ ) is the total of  $\lambda H_i$  and  $\lambda L_i$  as express in (1).

## International Journal of Engineering and Innovative Technology (IJEIT)

Volume 3, Issue 4, October 2013 (1)

$$\lambda = \sum_{i=0}^{N} \lambda H_i + \sum_{i=0}^{N} \lambda L_i$$

(1)

The number of maximum cells,  $P_{max}$  which is generated in one-time slot is depending on the traffic load,  $\rho$  which is equal to the total traffic load,  $\lambda$  and the number of port used. N. The relationship is shown in (2).

$$P_{\text{max}} = N \times \rho \tag{2}$$

In this simulation model, the cells are generated randomly to all destination port. Fig. 3 shows the address packet generation in the arrival process for hot-spot pattern and COI pattern.

```

IF (Hot-Spot Traffic)

FOR (port = 1 to N) DO

IF (random number < traffic load) THEN

Destination address = Hot-spot port

No destination address;

ENDIF

}

ELSE IF (COI traffic)

FOR (port = 1 to N) DO

IF (random number < traffic load) THEN

Destination address = random number * COI port;

ELSE

No destination address:

```

Fig. 3: Address packet generation in arrival process.

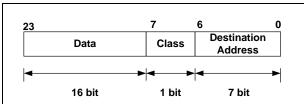

Fig. 4 shows the packet format for the input buffer in the multi-class switch. There are 24 bits in this packet. The first 8 bits are the header with the first 7 bits is the destination address and the nest 1 bit is used for the class. The others 16 bits are for data.

Fig. 4: Packet format for input buffer multi-class switch.

Each generated cell is classified as either high-priority class or low-priority class based on the traffic type. The highpriority cell is tagged with 1, and the low-priority cell is tagged with 0. Then, the cell is sent to FIFO while waiting to be served. The Class 1 cell is sent to FIFO H1, and the Class 0 cell is sent to FIFO L1. The HoL for Class 1 and Class 0 is in the queue until it is served. In general, the HoL scheduler will choose the cell in Class 1 since it has high-priority cells. In the case when both threshold values are achieved, the HoL scheduler will choose the Class 0 cells even in the presence of Class 1 cell.

The pseudo code for input buffer with HoL output

scheduling is shown in Fig. 5. When HoL for Class 1 is not empty, and the threshold value setting is applicable for both parameters, the HoL output will choose HoL packet from Class 0 instead of Class 1.

After HoL is selected, it will compete with another cell from another input port. The scheduler is using round robin policy with priority to select the cell in HoL for departure.

In departure phase, delays for Class 1 and Class 0 cells are calculated to measure the switch performance.

```

IF (HoL Class 1 not empty)

IF (N_b > T_N) \&\& (P_{TSC0} > T_P)

HoL_out = HoL Class 0;

ELSE

HoL_out = HoL Class 1;

HoL_out = HoL Class 0;

```

Fig. 5: Pseudo code for HoL scheduler.

#### IV. RESULTS AND DISCUSSION

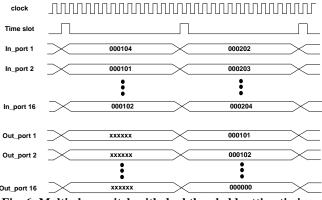

The proposed switch architecture is then implemented in the hardware simulation. Hardware timing simulations consist of the incoming and outgoing cells of the multi-class switch is shown in Fig. 6. It can be seen that there is new incoming cell at every time slots. After the cells have been processed, only the successful cell is allowed to depart. The rest of the cells must be waiting for their turns. The output cell timing is used to calculate the total means delay for Class 1 and Class 0.

Fig. 6: Multi-class switch with dual threshold setting timing simulation.

#### A. Total Mean Delay

The total mean delay with different threshold setting is calculated based upon the assumption that the arrival cells in a slot are independent and identically to the Bernoulli distributed processes. The total delay for each cell, D can be expressed as in (3) with  $T_q$  is the waiting time for the cell in the queue, T<sub>HoL</sub> is the waiting time for the cell in HoL, and T<sub>s</sub> is the delay in services.

$$D = T_a + T_{HoL} + T_s \tag{3}$$

In the hardware analysis, the total delay for each cell can be defined as the time for one cell being processed through

## ${\bf International\ Journal\ of\ Engineering\ and\ Innovative\ Technology\ (IJEIT)}$

Volume 3, Issue 4, October 2013

$$D = T_{out} - T_{in}$$

(4)

The system from the arrival time to the departure time. This is shown in (4) with  $T_{\rm in}$  is the cell arrival time and  $T_{\rm out}$  is the cell departure time. Then, the mean delay for single port Class C priority,  $D_{PC}$  can be calculated as in (5) with  $L_c$  is the total number of cells for Class C priority.

$$D_{PC} = \frac{\sum_{i=1}^{L_{c}} (D_{i})}{L_{c}}$$

(5)

By using the mean delay for single port Class C priority as in (5), the total mean delay for the whole system with N number of node, E(D) can be calculated as in (6).

$$E(D) = \frac{\sum_{i=1}^{N} (D_{PC})}{N}$$

(6)

#### B. Threshold Setting

Probability on the threshold serving low-priority cell  $(P_{TSC0})$  can be defined as the amount of delay allowed for the low-priority cell which is based upon the delay requirement while the number of queue cell  $(N_b)$  can be defined as the minimum traffic load that needs to be adjusted. Since the threshold setting is depending to these two parameters, the threshold setting will influence the delay performance of the system.

The probability of threshold serving class can be calculated as in (7) with  $P_{TSC0}$  is the probability of threshold serving Class 0,  $T_P$  is the threshold value in integer, and R is the size of a random number generator.

$$P_{_{TSC0}}=\frac{T_{_{P}}}{2^{_{R}}} \eqno(7)$$

The threshold value,  $T_{_{P}}$  must be larger than  $2^{R}\!/\!2$  to ensure

The threshold value,  $T_P$  must be larger than  $2^R/2$  to ensure the serving probability for Class 1 is better than Class 0.

## C. Non-Uniform Traffic

In this paper, two types of non-uniform traffic patterns; hot spot traffic pattern and the community-of-interest traffic pattern are used to analyze the performance of the switch. In non-uniform traffic, the traffic loads are not equally distributed to all port. There is a large number of non-uniform traffic patterns, depending upon the switch size.

#### 1) Hot-Spot Traffic Pattern

In the hot spot traffic pattern, all the arrival cells are destined to one destination port only [22], [23] as shown in Fig. 7.

Fig. 7: The hot-spot traffic pattern

The total of departure rate, *Y* with input port *i* at the hot spot port (output port 1) is equal to 1 as express in (8). This traffic pattern will create enormous delay at the hot-spot location.

$$\sum_{i=1}^{N} Y_{i,1} = 1 \tag{8}$$

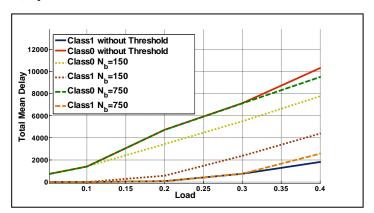

The analysis in the hot-spot traffic pattern for both Class 1 and Class 0 cells is done under two conditions. The first condition is under fixed  $P_{TSCO}$  with varying Nb, and the second condition is under fixed  $N_b$  with varying  $P_{TSCO}$ . These two conditions are selected to observe the threshold effect of the system with emphasis on the total mean delay.

Fig. 8 shows the plotted graph for the Class 1 and Class 0 total mean delay under the first condition. The probability of serving Class 0,  $P_{TSC0}$  is fixed at 60%. From the graph, it can be seen that changes start to occur when the load equal to 0.1 for the number of queue cells,  $N_b$  equal to 150 and at 0.3 for  $N_b$  equal to 750.

Fig. 8: Total mean delay for Class 1 and Class 0 with  $P_{\rm TSC0}$  fixed at 60% under hot-spot traffic.

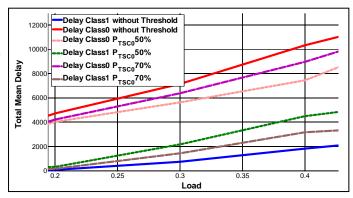

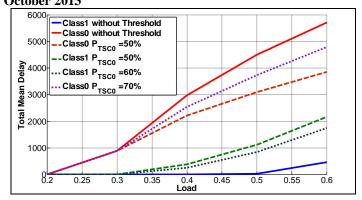

Fig. 9 shows the simulation graph for the Class 1 and Class 0 total means delay under the second condition. The graph is plotted against the number of queue cell  $N_b$  is fixed at 300. From the graph, it can be seen that a bigger variation delay starts when the load is equal to 0.2.

Fig. 9: Total mean delay for Class 1 and Class 0 with  $N_b$  fixed at 300 under hot-spot traffic.

#### 2) Community-of-Interest (COI) Traffic Pattern

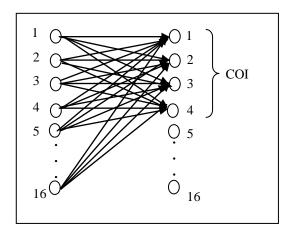

In the community-of-interest traffic pattern, all the arrival cells are destined to a group of ports in the switch [24]-[26].

## International Journal of Engineering and Innovative Technology (IJEIT) Volume 3, Issue 4, October 2013

In this case, the COI size is limited to 4 output ports, and all the input cells are destined to this COI as shown in Fig. 10.

Fig. 10: The COI traffic pattern.

The total departure rate, *Y* with input port *i* and output port *j* at COI location (output port 1 to 4) is equal to 1 as express in (9).

$$\sum_{i=1}^{N} \left( \sum_{j=1}^{4} Y_{i,j} \right) = 1$$

(9)

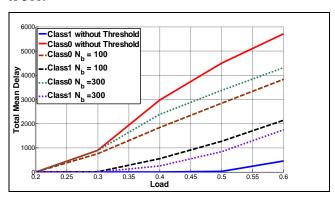

The analysis on the COI traffic pattern for both Class 1 and Class 0 cells is done under two conditions as the analysis for the hot spot traffic pattern. The first condition is under fixed  $P_{TSC0}$  with varying Nb, and the second condition is under fixed  $N_b$  with varying  $P_{TSC0}.$  These two conditions are selected to observe the threshold effect on the system under a different non-uniform traffic model.

In Fig. 11, a simulation graph for Class 1 and Class 0 total mean delay is plotted against the probability of serving Class 0,  $P_{TSC0}$  is fixed at 60%. From the graph, it can be seen that changes start to occur when the load is equal to 0.2 for the number of queue cells,  $N_b$  equal to 100 and at 0.3 for  $N_b$  equal to 300.

Fig. 11: Total mean delay for Class 1 and Class 0 with  $P_{\rm TSC0}$  fixed at 300 under COI traffic.

In the Fig. 12, simulation graph for the Class 1 and Class 0, total mean delay is plotted against the number of queue cell  $N_b$  is fixed at 300. From the graph, it can be seen that a bigger variation delay starts when the load is equal to 0.3.

Fig. 12: Total mean delay for Class 1 and Class 0 with  $N_{\text{b}}$  fixed at 300 under COI traffic.

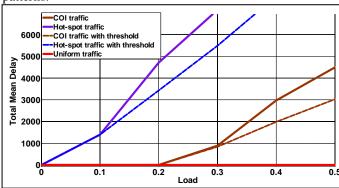

Fig. 13 shows the delay performance on Class 0 total mean delay under uniform and non-uniform traffic condition. It can be seen that usage of threshold has improved the total mean delay of the non-uniform traffics for both traffic patterns.

Fig. 13: Total mean delay for Class 0 under different traffic characteristics.

#### V. CONCLUSION

The simulation results have shown that dual threshold setting has reduced the total mean delay for the low-priority cell (Class 0) and at the same time minimized the delay increment for the high-priority cell (Class 1) under the non-uniform traffic. The number of queued cell ( $N_b$ ) which defines the minimum traffic load needs to be adjusted. The value of  $N_b$  is different depending upon the type of traffic.

Probability on threshold serving the low-priority cell (P<sub>TSC0</sub>) value defines the amount of delay allowed for the low-priority cells which is depending upon the delay requirement of the high- priority cells. The P<sub>TSC0</sub> parameter will increase the serving probability for Class 0 cells. By combining both parameters, the threshold setting can be used to identify the traffic load to start serving low-priority cell and the permitted variation delay.

#### REFERENCES

[1] A. A. Abdul Rahman, K. Seman and K. Saadan, "Multi-class scheduling technique using dual threshold," 8<sup>th</sup> Asia-Pacific Symposium on Information and Telecommunication Technologies (APSITT 2010), pp. 1-5, June 2010.

### International Journal of Engineering and Innovative Technology (IJEIT) Volume 3, Issue 4, October 2013

- [2] M. G. Hluchyj and M. J. Karol, "Queuing in high-performance packet switching," IEEE Journal on Selected Areas in Communications, vol. 6, no. 9, pp. 1587-1597, August 2002.

- [3] M. G. Hluchyj and M. J. Karol, "Queuing in space-division packet switching," IEEE INFOCOM Networks: Evolution or Revolution Proceedings, pp. 334-343, Mar 1988.

- [4] Hakyong Kim and Kiseon Kim, "Performance analysis of the multiple input-queued packet switch with the restricted rule," IEEE/ACM Transaction on Networking, vol. 11, no. 3, pp. 478-487, June 2003.

- [5] J. Y. Hui and E. Arthurs, "A broadband packet switch for integrated transport," IEEE Journal on Selected Areas in Communications, vol. 5, no. 8, pp. 1264-1273, January 2003.

- [6] J. Kleban and H. Santos, "Packet dispatching algorithms with the static connection patterns scheme for three-stage buffered close-network switches," IEEE International Conference on Communications (ICC'07), pp. 6319-6324, June 2007.

- [7] M. G. Hluchyj and M. J. Karol, "Using a packet switch for circuit-switched traffic: A queuing system with periodic input traffic," IEEE Trans. on Communications, vol. 37, no. 6, pp. 623-625, June 1989.

- [8] Y. Oie, M. Murata, K. Kubota and H. Miyahara, "Effect of speedup in no blocking packet switch," IEEE International Conference on Communications, pp. 410-414, June 1989.

- [9] MinJi Kim, J. K. Sundararajan, M. Medard, A. Eryilmaz and R. Kotter, "Network coding in a multicast switch," IEEE Transactions on Information Theory, vol. 57, no. 1, pp. 436-460, January 2011.

- [10] J. H. Patel, "Performance of processor-memory interconnections for multiprocessors," IEEE Transaction on Computers, vol. C-30, no. 10, pp.771-780, October 1981.

- [11] Rongsen He and J. G. Delgado Frias, "Fault tolerant interleaved switching fabrics for scalable high-performance routers," IEEE Transaction on Parallel and Distributed Systems, vol. 18, no. 12, pp. 1727-1739, December 2007.

- [12] A.K. Gupta and N.D. Georganas, "Priority performance of ATM packet switches," 1<sup>1th</sup> Annual Joint Conference of the IEEE Computer and Communications Societies, IEEE INFOCOM, pp. 727-733, May 1992.

- [13] L. Li, C. Hu and P.Liu, "Maximum throughput of an input queuing packet switch with two priority classes," IEEE Transaction on Communications, vol. 42, no. 12, pp. 3095-3097, December 1994.

- [14] Y.M. Lin and J.A. Silverster, "Priority queuing strategies and buffer allocation protocols for traffic control at an ATM integrated broadband switching system," IEEE Journal on Selected Areas in Communications, vol. 9, no. 9, pp. 15241536, December 1991.

- [15] A. Y. Lim and J. Kobza, "Analysis of a delay-dependent priority discipline in a multi-class traffic packet switching node," IEEE INFOCOM Networks: Evolution or Revolution Proceedings, pp. 889-898, Mar 1988.

- [16] B. Foo and M. Van Der Schaar, "A queuing theoretic approach to processor power adaptation for video decoding systems," IEEE Transactions on Signal Processing, vol. 56, no. 1, pp. 378-392, January 2008.

- [17] J. S. Choi and C. K. Un., "Delay performance of an input queuing packet switch with two priority classes," IEE Proceedings-Communications, vol. 145, no. 3, pp. 141-144, June 1998.

- [18] H. Yoon, M. T. Liu, K. Y. Lee, and Y. M. Kim, "The knockout switch under nonuniform traffic," IEEE Transactions on Communications, vol. 43, no. 6, pp. 2149-2156, June 1995.

- [19] T. K. C. Chan and Y. W. Leung, "Homogeneous and Heterogeneous subnetting for constructing all-optical multifiber networks," Journal of Light wave Technology, vol. 27, no. 13, pp. 2271-2281, July 2009.

- [20] S. Q. Li, "Nonuniform traffic analysis on a nonblocking space-division packet switch," IEEE Transactions on Communications, vol. 38, no. 7, pp. 1085-1096, July 1990.

- [21] R. Venkatesan, "Performance analysis of kappa networks and enlarged kappa networks under uniform and non-uniform traffic," Canadian Conference on Electrical and Computer Engineering, pp. 829-832, September 1994.

- [22] A. Pombortsis and C. Halatsis, "Performance of crossbar interconnection networks in presence of `hot spots'," Electronic Letters, vol. 24, no. 3, pp. 182-184, February 1988.

- [23] N. Mirfakhraei and T. Yongqun, "Performance analysis of Benes networks under nonuniform traffic," IEEE International Conference on Communications, pp. 1669-1673, June 1996.

- [24] A. J. Kalafut, J. Van Der Merwe, and M. Gupta, "Communities of interest for internet traffic prioritization," IEEE INFOCOM Workshops 2009, pp. 1-6, April 2009.

- [25] N. Mir, "Analysis of nonuniform traffic in a switching network," 7<sup>th</sup> International Conference on Computer Communications and Networks, pp. 668-672, October 1998.

- [26] Supriyanto, R. Budiarto, R. K. Murugesan and S. Ramadass, "CRC extension header (CEH): A new model to handle transmission error for IPv6 packets over fiber optic links," IEEE Symposium on Industrial Electronics & Applications (ISIEA), pp. 569-573, October 2009.

#### **AUTHOR BIOGRAPHY**

**Dr. Abdul Aziz Abdul Rahman** is a Senior Researcher at Telekom Research and Development Centre, Cyberjaya, Malaysia. He received B. Eng. degree from the Universiti Teknologi Malaysia in 2001. He later received a Master Degree in 2002 from Universiti Teknologi Malaysia and Ph.D in 2013 from the Universiti Sains Islam Malaysia (USIM). His current research interest is in switching and routing, network protocol, and network performance modeling.

**Dr. Kamaruzzaman Seman** is a professor at Faculty of Science and Technology, Universiti Sains Islam Malaysia (USIM). He received B. Eng. degree from the Universiti Teknologi Malaysia in 1985. He later received a Master Degree in 1986 from University of Essex, UK and Ph.D in 1994 from the University of Strathclyde, Glasglow, UK. His current research interest is in switching and routing, network protocol, and network performance modeling.

ISSN: 2277-3754

## ISO 9001:2008 Certified

International Journal of Engineering and Innovative Technology (IJEIT) Volume 3, Issue 4, October 2013

**Dr. Kamarudin Saadan** is a Senior Fellow at Faculty of Science and Technology, Universiti Sains Islam Malaysia (USIM). He received B. Eng. degree from the Universiti Kebangsaan Malaysia in 1973. He later received a Master Degree in 1977 from University of London, UK and Ph.D in 2000 from Universiti Kebangsaan Malaysia. His current research interest is in software quality assurance, information assurance and knowledge management.

**Dr. Azreen Azman** is a Senior Lecturer at Faculty of Computer Science and Information Technology, Universiti Putra Malaysia (UPM). He received Bachelor IT (Hons) from the Multimedia University in 1999. He later received a Ph.D in 2007 from University of Glasglow, UK. His current research interest is in browsing model, web information retrieval, data mining and knowledge discovery, relevance feedback learning and decision modeling.

Fatimah Salim is a lecturer at UTM Razak School, Universiti Teknologi Malaysia Kuala Lumpur. She received B. Eng. degree in 2002 and MEE in 2003 from the Universiti Teknologi Malaysia. She is currently working toward the Ph.D degree in the Faculty of Electrical Engineering, Universiti Teknologi Malaysia, Malaysia. Her current research interest is in power quality and power system analysis.